Select the IP Assignment option that you want to use ( DHCP or Static).

To configure the service processor’s IP address (optional):Ī.

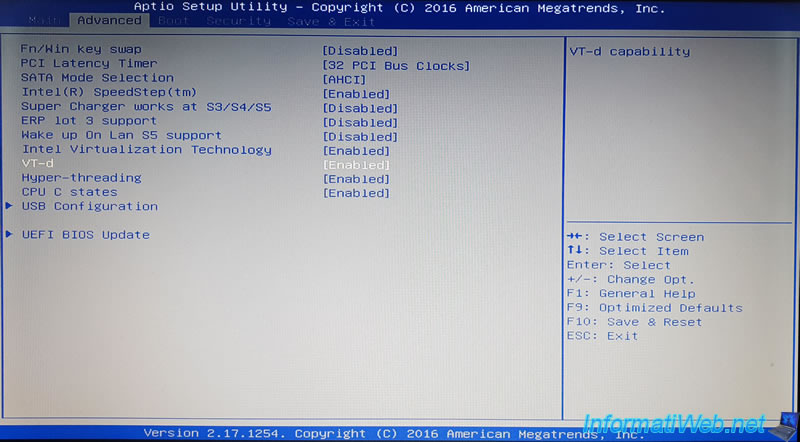

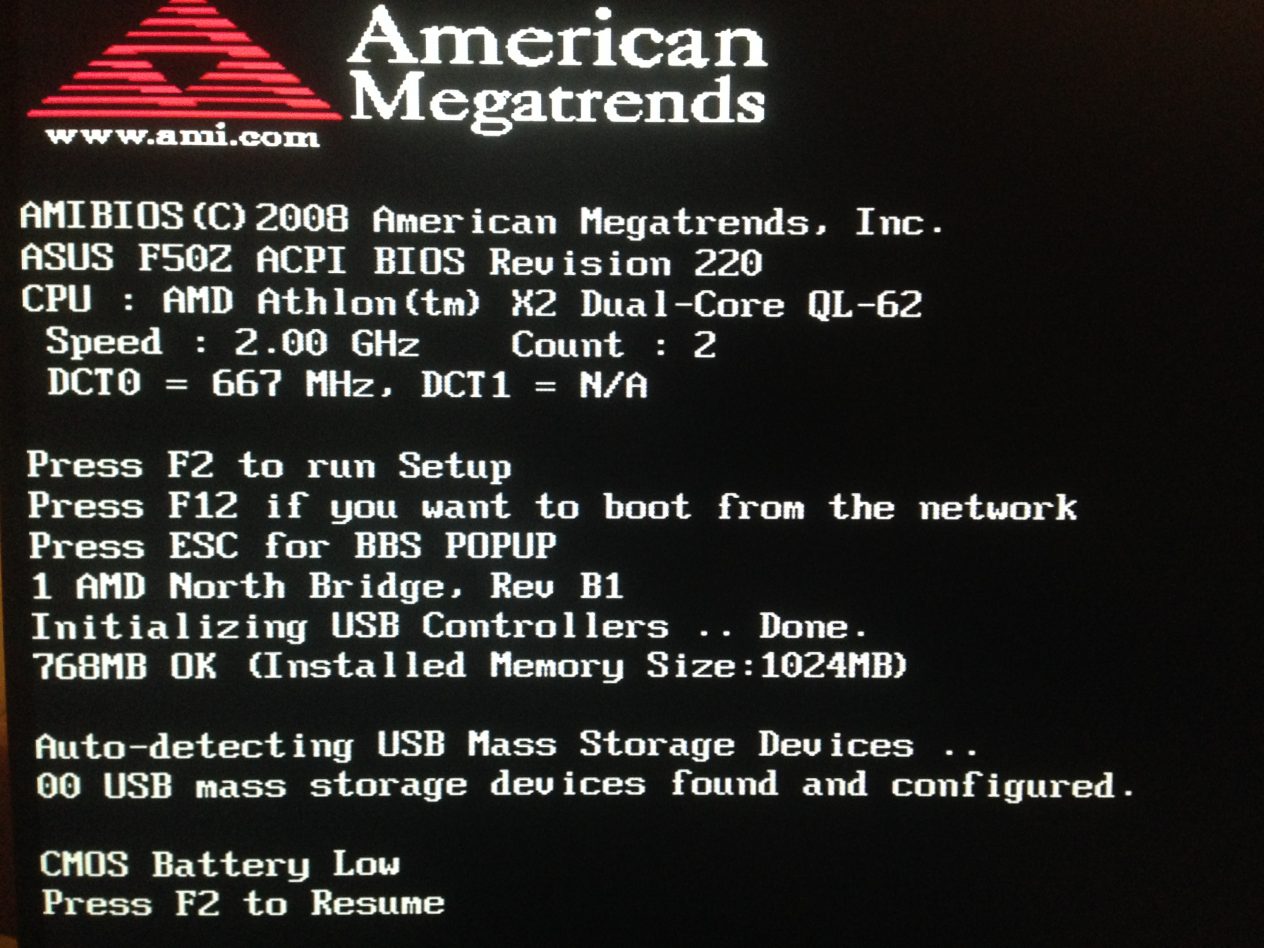

The LAN Configuration screen displays the service processor’s IP address.ĥ. The IPMI 2.0 Configuration screen is displayed.Ĥ. The Advanced Settings screen is displayed. Initialize the BIOS Setup utility by pressing the F2 key while the system is performing the power-on self-test (POST). Use the following instructions to access the service processor and redirect the console output so that the BIOS POST codes can be read.ġ. The BIOS polls the memory controllers for both correctable and uncorrectable memory errors and logs those errors into the service processor. You can cancel POST testing by pressing any key during POST.ģ. Note - Because the server can contain up to 64 MB of memory (128 MB for the X4440), the memory test can take several minutes. See Changing POST Options for more information.

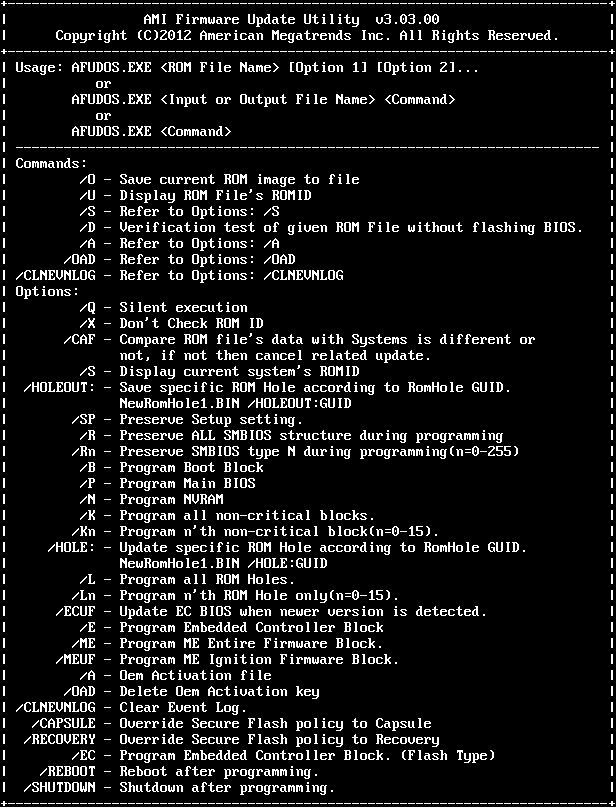

Note - Enabling Quick Boot causes the BIOS to skip the memory test. Once executing out of DRAM, the BIOS performs a simple memory test (a write/read of every location with the pattern 55aa55aa). The first megabyte of DRAM is tested by the BIOS before the BIOS code is shadowed (that is, copied from ROM to DRAM).Ģ. The BIOS POST memory testing is performed as follows:ġ. This section covers the following topics: An alternate method of displaying the POST codes is to redirect the output of the console to a serial port (see Redirecting Console Output). However, the codes are displayed as the self-test runs and scroll off of the screen too quickly to be read. These codes are displayed at the bottom right corner of the system’s VGA screen (once the self-test has progressed far enough to initialize the system video). The progress of the self-test is indicated by a series of POST codes. The basic devices required for the server to operate are checked, memory is tested, the LSI 1064 disk controller and attached disks are probed and enumerated, and the two Intel dual Gigabit Ethernet controllers are initialized. The system BIOS provides a rudimentary power-on self-test.

0 kommentar(er)

0 kommentar(er)